Stage : Accompagnement à la rédaction du plan de gestion des données

publié le 2 juin, 2025

1- Contexte

L’institut interdisciplinaire d’intelligence artificielle (IA) de Toulouse, appelé ANITI (Artificial and Natural Intelligence Toulouse Institute), est l’un des 9 IA clusters labélisés par France 2030. L’institut ANITI est porté par la Comue de Toulouse. Rassemblant environ 300 chercheurs et ingénieurs issus de 16 partenaires académiques et d’une trentaine de partenaires industriels, ANITI développe des technologies pour l’IA de confiance dans les secteurs d’application stratégiques suivants : mobilité / transports, industrie du futur, environnement. L’institut se situe au cœur des problématiques posées aujourd’hui par les technologies d’intelligence artificielle telles que la robustesse, l’explicabilité mais aussi l’acceptabilité par le public, l’éthique et la compréhension de leurs impacts sur la vie de nos concitoyens. Les activités de l’institut sont déclinées autour de 3 principaux volets :

- la recherche, avec 19 projets chaires de recherche,

- la formation avec l’ambition de doubler d’ici à 2029 le nombre d’étudiants formés à l’IA,

- le développement économique en accompagnant le transfert de technologies et le savoir-faire au sein des entreprises et en soutenant la création de start-ups.

ANITI souhaite mettre en place une politique de gestion et diffusion des données à l’échelle de l’institut, reposant sur son plan de gestion des données (PGD). Le stage vise à mettre en adéquation les préconisations du PGD et les pratiques de bonne gestion et diffusion des données. Le stage sera co-encadré entre ANITI et l’URFIST (Unité régionale de formation à l’information scientifique et technique).

2- Missions (à adapter selon la durée du stage) :

- Prendre connaissance du plan de gestion des données existant et assurer sa mise à jour.

- Recenser les pratiques en matière de gestion des données des établissements académiques partenaires d’ANITI et proposer des recommandations de gestion de données.

- Construire les outils d’accompagnement pour la bonne gestion et diffusion des données.

- Participer aux sessions de sensibilisation auprès des équipes de recherche d’ANITI.

Participer aux actions de l’équipe support d’ANITI et de l’URFIST.

3- Aptitudes requises

- Connaissance des plans de gestion de données et des règles de gestion et de diffusion

- Notions de propriété intellectuelle et de droit d’auteur

- Intérêt et connaissance du système d’enseignement supérieur et de recherche français

- Aptitudes au travail en équipe, bon relationnel

- Rigueur et sens de l’organisation

- Maîtrise des outils bureautiques

4- Conditions de stage

Stage conventionné avec gratification – durée souhaitée : 4 mois à partir de juin 2025

Temps plein – horaires en journée

Localisation géographique : Maison de la recherche et de la valorisation – 118 route de Narbonne – 31400 Toulouse. Déplacements à prévoir sur l’agglomération toulousaine.

Type de contrat : stage

Durée du contrat : 4 mois à partir de septembre 2025

Expérience : non

Lieu de travail :

Maison de la recherche et de la valorisation – 118 route de Narbonne – 31400 Toulouse

Quotité du travail : 100%

Pour postuler

CV et lettre de motivation à adresser à Amélie Barrio amelie.barrio@univ-toulouse.fr

Stage : LLM assisted Design of Complex Software Systems

– publié le 21 décembre, 2024

1- Context

Artificial intelligence and software engineering are different branches of computer science that can significantly contribute to each other. The rapid growth of Generative AI and particularly large language models (LLMs) enabled remarkable achievements for several code tasks based on text-prompting. For instance, it is possible to transform, add comments, think on, and summarize code. Most software experts agree that LLMs, such as those used by Copilot and ChatGPT, are expected to revolutionize the way in which software is developed. Many existing work are currently advocating the potential advantages generative AI models for writing code. However, the analysis of the current state of LLMs with respect to software modeling has received little attention. In our previous work, we suggested a new method for AI- guided software modeling. Promising results have been obtained with valuable insights for software engineering. Current LLMs are still not suitable to efficiently apply generative AI models for software modeling. Our findings show that, in contrast to code generation, the performance of the current versions of LLMs still suffer from several open issues such as insufficient training on specific languages, explicability, reliability, hallucination, scalability, resources consumption, and lack of real-time information. Those challenges once dealt with, LLMs would be insightful assistant for Software engineers. The results of this work would highly impact MBSE.

2- Internship goal :

The current internship deals with generative AI for Model Based Software Engineering (AI4MBSE). The hired student will proceed as follows. He/she will:

● Thoroughly study the aforementioned issues in order to state how LLMs can be invaluable to assist software modeling.

● Focuses on LLM prompting for real-world cases coming from industrial partners who are expert in embedded and railway systems.

● Develop a POC on a new prompting method.

● Validate the conducted results using existing LLMs.

3- Required Skills

- Good background on Software Engineering, formal methods, MBSE, and AI

- Good English level

4- Required Profil

Master 2 Computer Science or equivalent (engineering school).

5- Application Process

Interested candidates should submit the following meriem.ouederni@irit.fr:

- Detailed CV

- Cover letter explaining your motivation and relevant experience

- Academic transcripts

- References

4- Bibliographic References :

documents to

– MDE in the Era of Generative AI. A. ALAOUI MDAGHRI, M. Ouederni, and L. Chaari. Accepted to be published in VECOS’24 proceedings.

– Model-Driven Engineering. Douglas C. Schmidt. Computer Society-39.2 (2006) 25.

– Model-driven software engineering in practice. M. Brambilla, J. Cabot, M. Wimmer. Morgan and Claypool Publishers. 2017.

1 https://www.irit.fr

2 https://www.enseeiht.fr

3 https://www.inp-toulouse.fr

Type de contrat : stage

Durée du contrat : 4 to 6 months starting February/march 2024

Supervisors :

Meriem OUEDERNI and Lotfi CHAARI

Niveau d’études requis : Bac+5

Expérience : non

Lieu de travail : IRIT(1)/ENSEEIHT(2)/Toulouse Institut National Polytechnique(3)

Quotité du travail : 100%

Pour postuler

Interested candidates should submit the following meriem.ouederni@irit.fr:

• Detailed CV

• Cover letter explaining your motivation and relevant experience

• Academic transcripts

• References

Stage : Recherche en IA

Modèles génératifs combinant les approches des Modèles Basés sur l’Énergie (EBM) et des Réseaux Lipschitz – publié le 29 novembre, 2024

Entreprise et Équipe :

Le projet DEEL (Dependable, Explainable & Embeddable Learning) au sein de l’IRT Saint Exupéry et de l’IA Cluster Aniti vise à développer une Intelligence Artificielle de confiance pour son application dans les systèmes critiques. Avec plus de 17 partenaires industriels et 50 employés, DEEL est un projet franco- canadien qui contribue à la recherche en IA à travers la production d’articles scientifiques et au transfert de ces recherches vers le monde industriel via le développement de librairies open-source.

Le stage se fera avec des chercheurs de deux chaires de l’IA Cluster Aniti, la chaire CALM et la chaire C3PO.

Contexte :

Les Modèles Basés sur l’Énergie (Energy-Based Models, EBM), [6, 4, 5] sont une classe de modèles paramétriques qui définissent une fonction d’énergie pour

capturer la structure des données. En pratique, un modèle EBM définit une fonction scalaire E(x) pour des données x, où des valeurs plus faibles d’énergie correspondent à des configurations plus probables. Ces modèles sont utilisés dans diverses tâches telles que la génération de données [4], la reconnaissance robuste d’image [5], des tâches de raisonnement [3] et la planification de trajectoires en robotique [7].

Les réseaux Lipschitz sont une classe particulière de réseaux neuronaux qui respectent la propriété de réguralité Lipschitzienne (la variation de la sortie du reseau est bornée par une constante multipliée par la variation de son entrée). Ces réseaux sont connus pour leur robustesse aux perturbations adverses, leur stabilité, et leur explicatiblité [1, 8, 9].

Récemment, un papier publié par l’équipe DEEL [2] a étudié l’utilisation de réseaux Lipschitz pour l’estimation de densité d’une distribution. La proximité de cette approche avec celui de l’apprentissage des EBMs laisse entrevoir un grand intérêt de combiner les EBM avec des réseaux Lipschitz. En effet, la contrainte de Lipschitz permettra de garantir la stabilité des dynamiques dans le paysage énergétique définit par l’EBM. Cette propriété devrait permettre de stabiliser l’apprentissage des EBMS. et d’ouvrir de nouvelles perspectives pour des applications en apprentissage supervisé et non supervisé, où la robustesse et l’interprétabilité sont cruciales.

Missions :

- Étudier et comprendre les principes fondamentaux des Modèles Basés sur l’Énergie et des réseaux Lipschitz.

- Développer une architecture hybride et mettre en place un schéma d’apprentissage basé sur l’énergie et utilisant les réseaux Lipschitz.

- Analyser l’impact des contraintes Lipschitz sur les propriétés des EBM, notamment en ce qui concerne la généralisation et la capacité d’interprétation.

- Rédaction d’un rapport scientifique

Références :

[1] Cem Anil, James Lucas, and Roger Grosse. Sorting out lipschitz function approximation. In Interna- tional Conference on Machine Learning, pages 291–301. PMLR, 2019.

[2] Louis Béthune, Paul Novello, Guillaume Coiffier, Thibaut Boissin, Mathieu Serrurier, Quentin Vincenot, and Andres Troya-Galvis. Robust one-class classification with signed distance function using 1- lipschitz neural networks. In International Conference on Machine Learning, pages 2245–2271. PMLR, 2023.

[3] Yilun Du, Shuang Li, Joshua Tenenbaum, and Igor Mordatch. Learning iterative reasoning through energy minimization. In International Conference on Machine Learning, pages 5570–5582. PMLR, 2022.

[4] Yilun Du and Igor Mordatch. Implicit generation and modeling with energy based models. Advances in Neural Information Processing Systems, 32, 2019.

[5] David Duvenaud, Jackson Wang, Jorn Jacobsen, Kevin Swersky, Mohammad Norouzi, and Will Grath- wohl. Your classifier is secretly an energy based model and you should treat it like one. In ICLR 2020, 2020.

[6] Yann LeCun, Sumit Chopra, Raia Hadsell, et al. A tutorial on energy-based learning. 2006.

[7] Yunhao Luo, Chen Sun, Joshua B Tenenbaum, and Yilun Du. Potential based diffusion motion planning. arXiv preprint arXiv:2407.06169, 2024.

[8] Takeru Miyato, Toshiki Kataoka, Masanori Koyama, and Yuichi Yoshida. Spectral normalization forgenerative adversarial networks. In International Conference on Learning Representations, 2018.

[9] Mathieu Serrurier, Franck Mamalet, Alberto González-Sanz, Thibaut Boissin, Jean-Michel Loubes, and Eustasio Del Barrio. Achieving robustness in classification using optimal transport with hinge regularization. In Proceedings of the IEEE/CVF Conference on Computer Vision and Pattern Recognition, pages 505–514, 2021.

Profil :

Stage de fin d’études de niveau Bac+5 (Ingénieur, Master) en cursus Machine Learning, Mathématiques Appliquées, Informatique ou une discipline associée. Nous cherchons un.e candidat.e avec les compé- tences suivantes :

- Connaissances théoriques solides en Machine Learning et Deep Learning, en particulier sur les réseaux des neurones, la descente du gradient et l’optimisation mathématique.

- Expérience avec les librairies de Deep Learning modernes, en particulier PyTorch et/ou TensorFlow.

- Familiarité avec l’écriture scientifique sur LaTex.

- Être capable de lire, écrire et s’exprimer en anglais.

Type de contrat : stage

Durée du contrat : 6 mois

Niveau d’études requis : Bac+5

Expérience : non

Lieu de travail : Le stage se deroulera dans les locaux de l’IA Cluster Aniti, au B612 (3 rue Tarfaya, 31400 Toulouse)

Quotité du travail : 100%

Pour postuler

Adressez votre candidature à : franck.mamalet@irt-saintexupery.com en indiquant le titre du stage en sujet du mail. Le dossier de candidature devra être constitué d’un CV et les coordonnées d’une personne à qui demander une lettre de recommandation

Stage : Planification Optimale de missions de drones– publié le 29 novembre, 2024

Contexte :

Les flottes de drones (UAVs) sont de plus en plus utilisées pour diverses applications : surveillance, livraison, sauvetage, opérations militaires. Leur déploiement à grande échelle reste limité par des défis majeurs : gestion énergétique, coordination inter-drones, adaptation aux perturbations environnementales. Les approches actuelles manquent de flexibilité pour gérer simultanément ces contraintes tout en garantissant l’efficacité opérationnelle des différentes missions et la résilience du système.

Objectif :

Développer une architecture d’optimisation efficace et robuste pour la gestion énergétique et opérationnelle de flottes de drones, capable de :

- Optimiser la gestion énergétique globale en maximisant l’autonomie des drones via une planification intelligente des missions

- Gérer automatiquement les recharges et planification de remplacements des batteries sur plateformes terrestres mobiles

- Optimiser le déploiement spatial des drones en intégrant les contraintes géographiques et réglementaires (zones interdites, obstacles, limitations d’altitude)

- S’adapter aux conditions météorologiques : vent, pluie, brouillard, neige

- Orchestrer la coordination inter-flottes

Missions :

- Réaliser l’état de l’art des systèmes de gestion de flottes de drones et identifier les contraintes spécifiques par type d’environnement et de mission.

- Concevoir et développer une architecture d’optimisation basé sur l’IA (Apprentissage par renforcement Multi-Agent ou autre stratégie) pour la gestion des flottes de drones.

- Implémenter le système pour : la gestion énergétique, la coordination inter-flottes et les stratégies de résilience.

- Valider le système sur différents scénarios d’usage (surveillance, opérations urbaines, missions complexes)

Références :

[1] Thantharate, P., Thantharate, A., & Kulkarni, A. (2024). GREENSKY: A fair energy-aware optimization model for UAVs in next-generation wireless networks. Green Energy and Intelligent Transportation, 3(1), 100130

[2] Gadiraju, D. S., Karmakar, P., Shah, V. K., & Aggarwal, V. (2024). GLIDE: Multi-Agent Deep Reinforcement Learning for Coordinated UAV Control in Dynamic Military Environments. Information, 15(8), 477.

[3] Bouček, Z., & Flídr, M. (2024, September). Mission Planner for UAV Battery Replacement. In 2024 IEEE International Conference on Multisensor Fusion and Integration for Intelligent Systems (MFI) (pp. 1-6). IEEE.

Type de contrat : stage

Durée du contrat : 5-6 mois

Niveau d’études requis : Bac+5

Expérience : non

Lieu de travail : Toulouse

Quotité du travail : 100%

Pour postuler

Adresser CV + lettre de motivation :

Labsoft o.darricarrere@labsoft.fr

Thales : christelle.theulier.e@thalesdigital.io

Stage : Ingénieur développement d’algorithme d’optimisation «verte» des flux de trafic – publié le 29 novembre, 2024

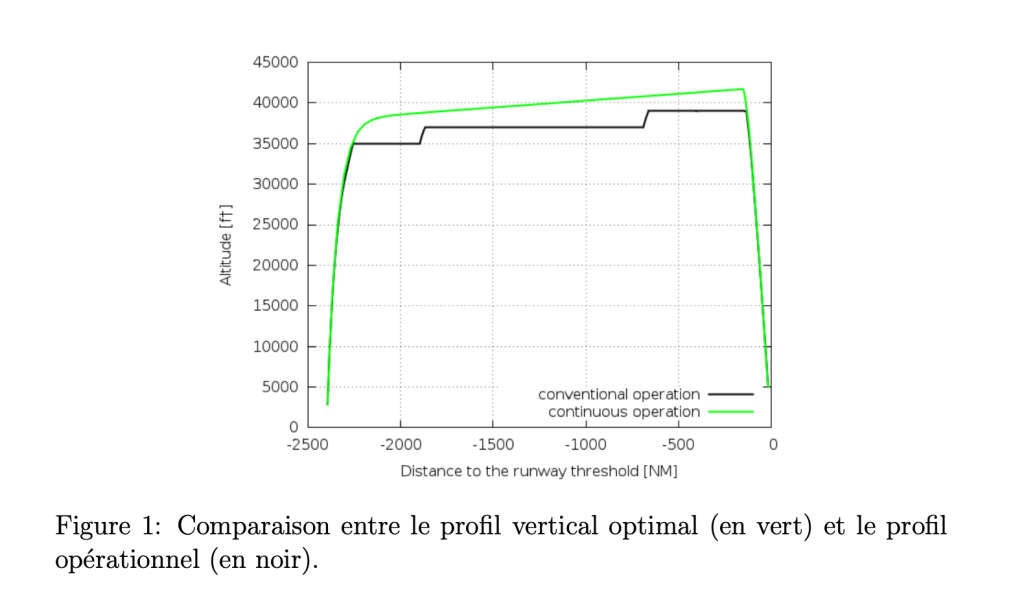

Afin d’assurer la capacité dans les centres de contrôle, l’espace aérien a été conçu de façon à fluidifier et à séparer le trafic, afin de garantir les niveaux de sécurité requis. Le trafic est ainsi structuré au niveau vertical (niveaux de vol), au niveau latéral (route aériennes) mais aussi au niveau temporel (régulation en vitesse à l’approche des TMA, “Miles en Trail aux États Unis). Si l’on considère, par exemple, le profil vertical optimal d’un avion de ligne (voir figure 1), ce dernier ne présente pas de niveaux de vol mais est constitué d’une montée et d’une descente continues (en vert sur la figure). Par contre, le profil opérationnel est contraint par des niveaux de vol afin d’aider les contrôleurs aériens à séparer les avions dans le plan vertical.

Dans le plan horizontal, les avions sont aussi contraints à suivre un réseau de routes qui permet de structurer le trafic pour les contrôleurs afin d’assurer la capacité des secteurs de contrôle. Ce réseau, associé à la sectorisation, permet de réduire le nombre de points de croisement et de localiser ces derniers dans la région centrale des secteurs afin d’augmenter l’efficacité des contrôleurs pour gérer le trafic. La nuit, lorsque le trafic est peu dense, il est très courant pour les contrôleurs de fournir des directes aux avions pour améliorer leur performance de vol. Lorsque le trafic augmente, les contrôleurs ont tendance à remettre les avions sur les routes et parfois à les contraindre en vitesse pour des questions de régulation dans les secteurs suivants (En route ou TMA). Si l’ensemble du trafic était opéré de façon à optimiser la consommation kérosène (routes optimales en fonction du vent, profil vertical optimal, profil de vitesse optimal), il serait impossible pour les contrôleurs, avec les outils actuels, de gérer efficacement ce type trafic et l’espace aérien se retrouverait très vite en sous capacité.

Les centres de contrôle, au cours d’une journée, sont essentiellement dimensionnés à la pointe et pendant certaines périodes, des secteurs du centre sont en surcapacité.

Dans ces secteurs, il serait alors possible, par le biais d’un outil d’aide à la décision, de proposer aux avions des trajectoires environnementalement efficaces au niveau pré-tactique. À partir d’un catalogue de trajectoires proposées par les compagnies aériennes classées du moins contraint au plus contraint (avec ou sans niveaux de vols, optimisée en fonction du vent, etc…), et des capacités des secteurs traversés par ces trajectoires, il est alors possible d’optimiser l’ensemble des trajectoires afin de minimiser l’impact environnemental du trafic, tout en respectant la capacité de l’espace aérien. Ces avions auraient alors un profil 4D optimisé mais aussi ils seraient plus complexes à gérer et devraient être pondérés d’un coefficient de complexité plus fort.

A l’échelle de quelques avions, un humain pourrait sélectionner ceux qui seraient susceptibles de bénéficier de trajectoires “vertes” , mais a` l’échelle d’un centre de contrôle, la complexité induite serait trop forte, et nous pro- posons dans ce stage de développer des algorithmes basés sur l’intelligence artificielle pour sélectionner les avions pouvant bénéficier de trajectoires plus efficaces au niveau environnemental, tout en assurant le respect des capacités des secteurs impactés. Cette approche pourra ensuite être déclinée au niveau Européen en collaboration avec le “Network Manager”.

Type de contrat : stage

Durée du contrat : 5-6 mois

Niveau d’études requis : Bac+5

Expérience : non

Lieu de travail :

Supervision :

Jacques Edeline (PO Green Ops) avec le support de Paul Lalisse (sur l’axe IA).

Quotité du travail : 100%

Pour postuler

Adresser CV + lettre de motivation :

Stage : Projet de fin d’études – Simulation des flux Bagages – publié le 29 novembre, 2024

Le pôle Data & Management Science de la Direction Générale des Opérations du Groupe ADP a pour objectifs d’identifier et de quantifier des gisements de valeur par l’utilisation de solutions d’aide à la décision pour améliorer la performance opérationnelle des plateformes du groupe et la performance d’entreprise de Groupe ADP.

La gestion des flux de bagages est essentielle à la performance de tout aéroport, et ce davantage pour un hub, ou plateforme de correspondances. À la suite d’une crise bagages majeure au cours de l’été 2022 au hub de Paris Roissy-CDG, le Groupe ADP a lancé un Plan Structurel de Robustesse. L’aide à la décision en matière de gestion des bagages fait partie des 4 piliers du plan, avec un mandat audacieux : « zéro bagage raté ». Un bagage raté est un bagage qui n’est pas acheminé sur le vol d’emport prévu.

Pour relever ce défi, Groupe ADP a construit une feuille de route sur 5 ans qui se décline en trois temps : l’exploitation des données historiques pour le diagnostic et les améliorations processuelles, le temps réel et la compréhension situationnelle, l’aide à la décision en réponse aux aléas opérationnels. Les cas d’usage traités vont de la compréhension des facteurs de sous-performance par des modèles économétriques, à la détermination de la capacité effective des systèmes de tri des bagages ou à l’optimisation des programmes de maintenance préventive de ces systèmes.

C’est dans ce cadre que Groupe ADP souhaite développer une capacité de simulation du fonctionnement des systèmes de tri et de la gestion des bagages dans son ensemble. Celle-ci s’appuie sur une chaîne logistique qui assure l’acheminement des bagages depuis des avions qui arrivent à des avions qui repartent, et mobilise une dizaine de systèmes de tri différents. La simulation d’un seul système de tri est le premier défi auquel nous nous confrontons.

Avant de travailler à la conception d’un simulateur, il sera essentiel de produire un état de l’Art du sujet. Ce dernier est d’ailleurs le premier résultat attendu du projet. En parallèle, et en s’appuyant sur des premiers travaux exploratoires sur la simulation des systèmes de tri, le projet a pour objectif d’identifier les axes d’amélioration prioritaires et d’en explorer les principaux. L’un des cas d’usage emblématique et à forte valeur ajoutée est de déterminer les capacités effectives des trieurs, avec ou sans incident de fonctionnement.

Enfin, Groupe ADP lance en parallèle une exploration des solutions de simulation du marché, sur lesquelles ce projet pourra s’appuyer.

Groupe ADP souhaite inscrire ce projet dans une perspective de travaux à long terme pouvant se poursuivre par un projet de thèse industrielle, de type CIFRE par exemple.

Type de contrat : stage

Durée du contrat : 5-6 mois

Niveau d’études requis : Bac+5

Expérience : non

Lieu de travail : CDG et CIFRE ensuite à Toulouse

Quotité du travail : 100%

Pour postuler

Adresser CV + lettre de motivation :

Florian.BERTOSIO@adp.fr

Rim.JABRI@adp.fr

Semi.GABTENI@adp.fr

Stage : Hybrid – AI-augmented – iterative methods – 28 novembre, 2024

1) Research project

Scientific machine learning (SciML) has significantly enhanced traditional numerical methods by streamlining computational modeling and offering cost-effective surrogate models. However, SciML surrogates suffer from the absence of explicit error control and the lack of reliability in practice. This project aims to address this limitation by developing novel hybrid iterative methods that combine the efficiency of SciML with the reliability of standard numerical approaches. In particular, we will investigate how to enhance trust-region algorithms for nonlinear optimization using operator learning approaches, e.g., DeepONets or FNOs.

Scientific environment

The candidate will join the international chair HAILSED at ANITI and the IRIT Laboratory (APO team) at ENSEEIHT (Toulouse-INP). The HAILSED chair, focusing on hybridizing AI and large-scale numerical simulations for engineering design, offers valuable opportunities to engage with experts in (scientific) machine learning, applied mathematics, scientific computing, numerical simulations, and high-performance computing (HPC). The candidate will also actively collaborate with researchers from ISAE-SUPAERO and IRT Saint Exup ́ery, enhancing their scientific development and interdisciplinary research profile.

Candidate’s profile

The candidate should be interested in computational science, applied mathematics, or related fields. Additionally, experience in the following areas is highly beneficial:

- Programming in Python

- Practical deployment of (Sci)ML applications within PyTorch, Tensorflow, JAX, etc.

- Knowledge of numerical optimization and iterative methods for solution of linear systems of equations (stationary iterative methods, Krylov methods)

- Working proficiency in English.

Type de contrat : stage

Durée du contrat : 5-6 months

Niveau d’études requis : Bac+5

Expérience : non

Lieu de travail : ENSEEIHT (2 Rue Charles Camichel, 31000 Toulouse, France)

Quotité du travail : 100%

Supervision :

Alena Kopanicakova (Toulouse-INP/ANITI)

Pour postuler

1. A comprehensive CV

2. A motivation letter detailing the applicant’s research interests and reasons for applying

Please send your complete application in one single PDF file to Alena Kopaniˇc ́akov ́a (alena.kopanicakova@toulouse- inp.fr). The call is open until the position is filled.

Stage : ÉCOLE NATIONALE DE LA MÉTÉOROLOGIE – Utilisation de réseaux de neurones informés par la physique (PINNs) pour le développement de paramétrisations dans ARP-GEM – 25 octobre, 2024

1) Description du sujet – livrables attendus

Même si des études récentes montrent qu’il est possible d’utiliser des résolutions plus fines pour des simulations climatiques, la majorité des modèles de climat utilisent une résolution horizontale de l’ordre de 150 km à 50 km. À ces résolutions, seuls les processus de grande échelle sont décrits par les équations primitives discrétisées. Pour représenter les processus de fine échelle, non explicitement résolus par le modèle, comme la convection profonde, la turbulence ou la microphysique, la démarche classique consiste à utiliser des paramétrisations physiques. Les paramétrisations physiques sont des ensembles d’équations, empiriques ou théoriques, développées à partir d’une combinaison de données issues d’observations, de modèles conceptuels, de résultats de modèles à haute résolution, et/ou d’approches théoriques.

Une nouvelle méthode permettant de développer de nouvelles paramétrisations consiste à utiliser des techniques de machine learning, en particulier des réseaux de neurones (NN). Les NN pourraient réduire certains biais connus des paramétrisations physiques. Mais la cohérence physique des paramétrisations NN peut être insuffisante. Cela se traduit alors par l’apparition de biais (et/ou d’explosion numérique) dans les simulations climatiques.

Il existe une famille de techniques permettant d’implémenter des contraintes physiques aux NN pendant l’apprentissage, appelée « NNs informés par la physique » (ou « physics informed neural networks », PINNs). Dans ce stage, nous proposons d’explorer ces approches dans le cadre du développement d’une paramétrisation NN pour la convection profonde. Pour ce faire, nous utiliserons la paramétrisation de convection profonde de notre modèle comme cadre idéal de travail. Il s’agira de mettre en place et tester la valeur ajoutée de contraintes physiques, à travers l’utilisation d’une des deux méthodes suivantes : (i) via un terme de pénalité ajouté à la loss pendant l’apprentissage ou (ii) en ajoutant une couche spécifique à la fin du NN dont les paramètres sont imposés manuellement.

Les cadre de travail permettant la construction de l’échantillon d’apprentissage est en place, et la réalisation de tests en ligne de paramétrisations NN est d’ores et déjà possible et a été testé. Un planning prévisionnel du projet pourrait être le suivant :

(1) lecture de quelques articles clés pour mieux comprendre le problème ;

(2) construction de l’échantillon d’apprentissage à partir des données brutes ;

(3) réalisation des apprentissages en implémentant la ou les contraintes physiques ;

(4) comparaison des résultats obtenus avec chacune des méthodes (et avec la version ‘sans contraintes physiques’);

(5) test de la paramétrisation obtenue en ligne

Les tests en ligne se feront dans le modèle ARP-GEM1, une version d’ARPEGE/IFS, optimisée et contenant une physique à l’état de l’art (Saint-Martin et Geoffroy, 2024 ; Geoffroy et Saint-Martin, 2024, en préparation) pour laquelle un interfaçage souple entre le modèle de climat et la paramétrisation NN a été récemment développée (Balogh et al., 2024, en préparation).

Suivant l’avancement du travail, d’autres pistes pour une utilisation optimale des algorithmes de machine learning pour la modélisation climatique pourront être explorées.

Références sur le sujet

– Sur l’utilisation des PINNs pour les paramétrisations : Beucler, T., Pritchard, M., Rasp, S., Ott, J., Baldi, P., & Gentine, P. (2021). Enforcing Analytic Constraints in Neural Networks Emulating Physical Systems. Physical Review Letters, 126(9). https://doi.org/10.1103/physrevlett.126.098302

– Sur les paramétrisations NN : Gentine, P., Pritchard, M., Rasp, S., Reinaudi, G., & Yacalis, G. (2018). Could machine learning break the convection parameterization deadlock? Geophysical Research Letters, 45, 5742–5751. https://doi.org/10.1029/2018GL078202

– Sur les PINNs : Raissi, M., Perdikaris, P., & Karniadakis, G. E. (2017, November 28). Physics Informed Deep Learning (Part I): Data-driven Solutions of Nonlinear Partial Differential Equations. arXiv.org. https://arxiv.org/abs/1711.10561

Balogh, B., Saint-Martin, D., & Ribes, A. (2021). A toy model to investigate stability of AI-based dynamical systems. Geophysical Research Letters, 48, e2020GL092133. https://doi.org/10.1029/2020GL092133

Balogh, B., Saint-Martin, D., & Ribes, A. (2022). How to calibrate a dynamical system with neural network based physics? Geophysical Research Letters, 49, e2022GL097872. https://doi.org/10.1029/2022GL097872

Balogh, B., Saint-Martin, D., & Geoffroy, O. (2024). Developing a Fortran-Python Interface in ARP- GEM: Application to a Deep Convection Neural Network. Submitted to AIES.

Saint-Martin, D., & Geoffroy, O. (2024). The ARP-GEM Global Atmospheric Model Version 1, part I: Model Description and Speed-Up Analysis. https://arxiv.org/abs/2409.19083v1

Geoffroy, O., & Saint-Martin, D. (2024). The ARP-GEM global atmospheric model version 1, part II : multiscale evaluation from 50 to 6 km. https://arxiv.org/abs/2409.19089

Prérequis

Un bon niveau en python est souhaité, avec des bases en machine learning. Quelques bases en fortran peuvent être utiles. Des bases en sciences du climat sont un plus.

2) lieu du stage, durée ou période

Lieu du stage : CNRM

Durée : 5 à 6 mois entre février 2025 et août 2025

Type de contrat : stage

Durée du contrat : 6 mois

Niveau d’études requis : Bac+5

Expérience : non

Lieu de travail : CNRM Toulouse

Quotité du travail : 100%

Supervision :

Blanka Balogh (CNRM), David Saint-Martin (CNRM) et Olivier Geoffroy (CNRM)

Pour postuler

Adresser CV + lettre de motivation :

blanka.balogh@meteo.fr

Stage : ÉCOLE NATIONALE DE LA MÉTÉOROLOGIE – Développement et évaluation d’un passage à l’échelle des prévisions Arome sur l’Europe avec des méthodes d’Intelligence Artificielle Générative – 25 octobre, 2024

1) Description du sujet – livrables attendus

L’utilisation de l’intelligence artificielle (IA) pour la Prévision Numérique du Temps (PNT) se démocratise progressivement depuis plusieurs années. Les algorithmes d’apprentissage profond et les approches génératives ont d’ailleurs récemment fait leur preuve dans ce domaine d’application. Désormais, ces méthodes ont la capacité de produire des champs physiques avec une certaine cohérence physique, pour un coût numérique très inférieur aux méthodes classiques d’intégration numérique.

Le stage proposé se place dans le cadre de Destination Earth (DestinE). DestinE est une initiative de la Commission européenne dans le cadre du programme EU Digital Europe. Ce projet vise à déployer plusieurs jumeaux numériques de la Terre, qui aideront à surveiller et à prévoir les changements environnementaux et l’impact humain, afin de développer et de tester des scénarios qui soutiendraient le développement durable et les politiques européennes correspondantes pour le Green Deal. L’IA, et en particulier l’apprentissage profond, sont un des axes développés dans DestinE.

Le travail durant le stage sera à destination du projet DE_371, auquel l’équipe d’accueil participe. L’objectif du projet DE_371 est de démontrer que des méthodologies utilisant les algorithmes d’IA à l’état de l’art peuvent aider à améliorer l’estimation de l’incertitude des prévisions, en permettant de produire des prévisions d’ensemble de grande taille et à haute résolution spatiale et temporelle.

L’objectif du travail proposé est d’utiliser des techniques d’IA dites génératives comme les Réseaux Antagonistes Génératifs (GAN) [1] pour améliorer les performances du système opérationnel de prévision d’ensemble Arome. L’équipe d’accueil a développé un prototype StyleGAN [2][3] capable de générer des membres Arome physiquement cohérents sur un quart sud-est de la France et pour quelques variables de surface. Ce stage se propose d’utiliser ce prototype comme base de développement. Les résultats encourageants mènent vers plusieurs pistes d’approfondissement et d’amélioration, qui feront l’objet du présent stage, parmi lesquelles :

-

Adaptation du modèle à une extension du domaine actuel.

-

Exploration de méthodes de Transfer Learning [4] sur le domaine nordique (Norvège, Suède).

-

Evaluation des prévisions StyleGAN sur des évènements à fort impact.

Le ou la stagiaire pourra disposer de moyens de calculs sur GPU importants (plate-forme Météo France et/ou super-calculateur EuroHPC), au sein d’une équipe expérimentée et motivée. Il ou elle bénéficiera des outils et méthodes déjà développés dans l’équipe. Ce stage sera l’occasion de développer ses compétences, notamment :

-

expérience de développement d’algorithmes d’apprentissage profond à l’état de l’art

-

manipulation d’une infrastructure de calcul haute-performance

-

gestion d’une base de code commune et ajout de fonctionnalités

-

intéractions avec des partenaires internationaux (centres météorologiques en Norvège et Suède)

Ce stage requiert un réel intérêt pour la prévision numérique du temps (des connaissances préalable à ce sujet seraient un plus mais ne sont pas nécessaire). De solides compétences en statistiques et une bonne maîtrise du langage Python seront également nécessaires. Une connaissance préalable du fonctionnement des réseaux de neurones profonds (en particulier des réseaux convolutifs CNN) est souhaitée. Une première expérience d’une bibliothèque de Deep Learning (PyTorch, TensorFlow, …) serait un plus.

Livrables attendus : codes, rapport, support de soutenance.

2) Lieu du stage, durée ou période

Ce stage de 6 mois se déroulera dans l’équipe Prévisibilité du Centre National de Recherche Météorologique (CNRM), à Toulouse. Des réunions régulières avec les ingénieurs du projet seront organisées.

3) Références bibliographiques

[1] Goodfellow, I., Pouget-Abadie, J., Mirza, M., Xu, B., Warde-Farley, D., Ozair, S., … & Bengio, Y. (2020). Generative adversarial networks. Communications of the ACM, 63(11), 139-144. https://dl.acm.org/doi/pdf/10.1145/3422622.

[2] Karras, T., Laine, S., Aittala, M., Hellsten, J., Lehtinen, J., & Aila, T. (2020). Analyzing and improving the image quality of stylegan. In Proceedings of the IEEE/CVF conference on computer vision and pattern recognition (pp. 8110-8119).https://openaccess.thecvf.com/content_CVPR_2020/papers/ Karras_Analyzing_and_Improving_the_Image_Quality_of_StyleGAN_CVPR_2020_paper.pdf

[3] Brochet, C., Raynaud, L., Thome, N., Plu, M., & Rambour, C. (2023). Multivariate Emulation of Kilometer-Scale Numerical Weather Predictions with Generative Adversarial Networks: A Proof of Concept. Artificial Intelligence for the Earth Systems, 2(4), 230006. https://doi.org/10.2496.

[4] Lee, D., Lee, J. Y., Kim, D., Choi, J., & Kim, J. (2022). Fix the noise: Disentangling source feature for transfer learning of StyleGAN. arXiv preprint arXiv:2204.14079. https://arxiv.org/pdf/2204.14079

Type de contrat : stage

Durée du contrat : 6 mois

Niveau d’études requis : Bac+5

Expérience : non

Lieu de travail : CNRM Toulouse et à distance

Quotité du travail : 100%

Supervision :

Victor Sanchez (CNRM), Angélique Bonamy (CNRM) et Laure Raynaud (CNRM)

Pour postuler

Adresser CV + lettre de motivation :

victor.sanchez@meteo.fr

Stage : EXPLORATION DES SYNERGIES ENTRE MÉTHODES STATISTIQUES ET FORMELLES POUR L’EXPLICABILITÉ DE L’INTELLIGENCE ARTIFICIELLE – 21 octobre, 2024

Dans ce stage, nous nous pencherons sur la synergie entre deux domaines essentiels de l’explicabilité de l’intelligence artificielle : L’explicabilité statistique et l’explicabilité formelle. L’explicabilité statistique, en particulier par l’attribution de caractéristiques, a été la pierre angulaire de l’identification des caractéristiques significatives contribuant à une prédiction. Cette méthode s’est avérée efficace pour diverses architectures neuronales, offrant une évolutivité et une application généralisée.

Cependant, le manque de garanties dans les méthodes statistiques a limité leur utilisation pratique dans l’industrie. Pour y remédier, notre projet de stage propose une analyse comparative des cartes de caractéristiques générées par les méthodes statistiques et les méthodes formelles. En examinant ces deux familles de techniques d’explicabilité, nous visons à combler le fossé entre la robustesse théorique et l’applicabilité pratique.

Ce projet sera évalué à l’aide d’un ensemble de données industrielles libres axées sur des scénarios d’atterrissage visuels. Les résultats pourraient potentiellement améliorer la fiabilité et la capacité d’action des méthodes d’explicabilité dans les applications du monde réel.

Idéalement, ce stage d’une durée de 6 mois commencera en Mars 2025 (la période est communiquée à titre indicatif, et pourra être revue).

Tasks and Accountabilities :

Votre tuteur/tutrice vous aidera à identifier vos objectifs professionnels et vous accompagnera dans le développement de vos compétences.

Vos principales activités seront les suivantes :

- Conduire un état de l’art des méthodes d’explicabilité statistique et formelle.

- Développer les algorithmes de mise en pratique des méthodes les plus pertinentes.

- Appliquer les méthodes à un cas d’usage industrie

Ce stage vous permettra notamment de développer les compétences suivantes :

- Connaissance des différentes méthodes d’explicabilité pour l’intelligence artificielle.

- Développement dans un cadre d’application industriel.

- Travail en équipe.

Required skills

Vous préparez actuellement un diplôme de niveau Bac +5 dans le domaine de l’intelligence artificielle ou une discipline apparentée?

Vous possédez les compétences suivantes :

-

- Expérience en python et framework Machine Learning/Deep Learning (e.g. Keras/Tensorflow)

- Expérience sur certaines méthodes d’explicabilité

- Excellent niveau de communication, travail d’équipe

Compétences linguistiques :

- Anglais : Intermédiaire

- Français : Avancé

Type de contrat : stage

Durée du contrat : 6 months

Niveau d’études requis : Bac+5

Expérience : non

Lieu de travail : Toulouse

Quotité du travail : 100%

Supervision :

Boumazouza Ryma (Airbus) et Ducoffe Mélanie (Airbus)

Pour postuler

Adresser CV + lettre de motivation :

ryma.boumazouza@airbus.com

melanie.ducoffe@airbus.com

Internship : FORMAL VERIFICATION OF MACHINE LEARNING ALGORITHMS ON ADVANCED AVIONICS HARDWARE – October 15, 2024

Machine Learning (ML) plays a pivotal role in the development of autonomous systems, including future generations of aircraft that will integrate advanced algorithms for enhanced capabilities, such as vision-based autonomous landing for drones and commercial aircraft. While these algorithms perform efficiently in cloud or data center environments, deploying them on autonomous vehicles presents significant challenges—especially in ensuring safety. In the field of aeronautics, every function, whether ML-based or not, must meet rigorous safety standards, even in the event of hardware failures.

Vision-based perception systems, which are critical for autonomous operations, demand immense computational power and high-bandwidth communications (e.g., from cameras). However, current avionics processors lack the necessary capacity to handle such workloads. As a result, new processing architectures, such as Component-off- the-shelf (COTS) GPUs and many-core processors, will be essential. Before these can be deployed, it’s crucial to study their hardware failure modes, understand how these failures could affect the ML algorithms they support, and develop safeguards to ensure safe execution.

Several existing works, such as [1], [2], and [3], have addressed these issues by formally modeling platform behavior in the presence of faults, along with the mitigation strategies designed to reduce the impact of these faults. These models can be analyzed using solvers to determine if the mitigations are sufficient to guarantee safe hardware operation under specified conditions.

Preliminary research has identified the Versatile Tensor Accelerator (VTA [4]) as a suitable candidate for further exploration of this problem. VTA is open hardware, meaning its hardware description is fully accessible and customizable. It is described using Chisel [5], an advanced high-level hardware description language built on Scala [6].

[1] Guinebert, I., Barrilado, A., Delmas, K., Galtié, F., & Pagetti, C. (2022, June). Quality of Fault Injection Strategies on Hardware Accelerator. In International Conference on Computer Safety, Reliability, and Security (pp. 222-236). Cham: Springer International Publishing.

[2]Faure-Gignoux, A, Delmas, K, Gauffriau, A, Pagetti, C. (2024) Methodology for formal verification of hardware.safety strategies using SMT. International conference on embedded software (EMSOFT)

[3] Dobis, A., Laeufer, K., Damsgaard, H. J., Petersen, T., Rasmussen, K. J. H., Tolotto, E., … & Schoeberl, M. (2023). Verification of chisel hardware designs with chiselverify. Microprocessors and Microsystems, 96, 104737.

[4] https://github.com/apache/tvm-vta [5] https://www.chisel-lang.org/

Tasks and Accountabilities :

The primary goal of this internship is to evaluate the effectiveness of a set of pre-selected formal verification methods on the VTA. The key steps include:

-

- Conducting a literature review to identify the most promising formal verification methods from the pre- selected set.

- Gaining proficiency with the toolset required for functional and cycle-accurate simulation of VTA executions.

- Developing a framework to run small portions of deep neural networks (DNNs) on both functional and cycle-accurate simulators.

- Extending the framework to verify formal properties using the selected methods.

- Assessing the expressiveness and scalability of the approach, initially focusing on specific parts of theVTA, and, if feasible, expanding to the full accelerator.

- Based on the experiments, formulating recommendations for future theoretical and practicaldevelopments required for full-scale safety validation of VTA-like accelerators.

Required skills

-

- Hardware description languages (advanced)

- Compilation, Computing architectures (intermediate)

- Formal verification (notions)

- Programming (advanced)

Desired period

March to September 2025

Type de contrat : stage

Durée du contrat : 5-6 months (march to September 2025)

Gratification : 624,22€/month

Niveau d’études requis : Bac+5

Expérience : non

Lieu de travail : ONERA Toulouse: 2 Av. Marc Pélegrin, 31000 Toulouse. (Toulouse)

Quotité du travail : 100%

Supervision :

Kevin Delmas (ONERA) and Anthony Faure-Gignoux (ONERA)

Pour postuler

Adresser CV + lettre de motivation :

Kevin.delmas@onera.fr

Anthony.faure-gignoux@onera.fr

Stage : ÉCOLE NATIONALE DE LA MÉTÉOROLOGIE – Développement et évaluation d’un passage à l’échelle des prévisions Arome sur l’Europe avec des méthodes d’Intelligence Artificielle Générative – 25 octobre, 2024

1) Description du sujet – livrables attendus

L’utilisation de l’intelligence artificielle (IA) pour la Prévision Numérique du Temps (PNT) se démocratise progressivement depuis plusieurs années. Les algorithmes d’apprentissage profond et les approches génératives ont d’ailleurs récemment fait leur preuve dans ce domaine d’application. Désormais, ces méthodes ont la capacité de produire des champs physiques avec une certaine cohérence physique, pour un coût numérique très inférieur aux méthodes classiques d’intégration numérique.

Le stage proposé se place dans le cadre de Destination Earth (DestinE). DestinE est une initiative de la Commission européenne dans le cadre du programme EU Digital Europe. Ce projet vise à déployer plusieurs jumeaux numériques de la Terre, qui aideront à surveiller et à prévoir les changements environnementaux et l’impact humain, afin de développer et de tester des scénarios qui soutiendraient le développement durable et les politiques européennes correspondantes pour le Green Deal. L’IA, et en particulier l’apprentissage profond, sont un des axes développés dans DestinE.

Le travail durant le stage sera à destination du projet DE_371, auquel l’équipe d’accueil participe. L’objectif du projet DE_371 est de démontrer que des méthodologies utilisant les algorithmes d’IA à l’état de l’art peuvent aider à améliorer l’estimation de l’incertitude des prévisions, en permettant de produire des prévisions d’ensemble de grande taille et à haute résolution spatiale et temporelle.

L’objectif du travail proposé est d’utiliser des techniques d’IA dites génératives comme les Réseaux Antagonistes Génératifs (GAN) [1] pour améliorer les performances du système opérationnel de prévision d’ensemble Arome. L’équipe d’accueil a développé un prototype StyleGAN [2][3] capable de générer des membres Arome physiquement cohérents sur un quart sud-est de la France et pour quelques variables de surface. Ce stage se propose d’utiliser ce prototype comme base de développement. Les résultats encourageants mènent vers plusieurs pistes d’approfondissement et d’amélioration, qui feront l’objet du présent stage, parmi lesquelles :

-

Adaptation du modèle à une extension du domaine actuel.

-

Exploration de méthodes de Transfer Learning [4] sur le domaine nordique (Norvège, Suède).

-

Evaluation des prévisions StyleGAN sur des évènements à fort impact.

Le ou la stagiaire pourra disposer de moyens de calculs sur GPU importants (plate-forme Météo France et/ou super-calculateur EuroHPC), au sein d’une équipe expérimentée et motivée. Il ou elle bénéficiera des outils et méthodes déjà développés dans l’équipe. Ce stage sera l’occasion de développer ses compétences, notamment :

-

expérience de développement d’algorithmes d’apprentissage profond à l’état de l’art

-

manipulation d’une infrastructure de calcul haute-performance

-

gestion d’une base de code commune et ajout de fonctionnalités

-

intéractions avec des partenaires internationaux (centres météorologiques en Norvège et Suède)

Ce stage requiert un réel intérêt pour la prévision numérique du temps (des connaissances préalable à ce sujet seraient un plus mais ne sont pas nécessaire). De solides compétences en statistiques et une bonne maîtrise du langage Python seront également nécessaires. Une connaissance préalable du fonctionnement des réseaux de neurones profonds (en particulier des réseaux convolutifs CNN) est souhaitée. Une première expérience d’une bibliothèque de Deep Learning (PyTorch, TensorFlow, …) serait un plus.

Livrables attendus : codes, rapport, support de soutenance.

2) Lieu du stage, durée ou période

Ce stage de 6 mois se déroulera dans l’équipe Prévisibilité du Centre National de Recherche Météorologique (CNRM), à Toulouse. Des réunions régulières avec les ingénieurs du projet seront organisées.

3) Références bibliographiques

[1] Goodfellow, I., Pouget-Abadie, J., Mirza, M., Xu, B., Warde-Farley, D., Ozair, S., … & Bengio, Y. (2020). Generative adversarial networks. Communications of the ACM, 63(11), 139-144. https://dl.acm.org/doi/pdf/10.1145/3422622.

[2] Karras, T., Laine, S., Aittala, M., Hellsten, J., Lehtinen, J., & Aila, T. (2020). Analyzing and improving the image quality of stylegan. In Proceedings of the IEEE/CVF conference on computer vision and pattern recognition (pp. 8110-8119).https://openaccess.thecvf.com/content_CVPR_2020/papers/ Karras_Analyzing_and_Improving_the_Image_Quality_of_StyleGAN_CVPR_2020_paper.pdf

[3] Brochet, C., Raynaud, L., Thome, N., Plu, M., & Rambour, C. (2023). Multivariate Emulation of Kilometer-Scale Numerical Weather Predictions with Generative Adversarial Networks: A Proof of Concept. Artificial Intelligence for the Earth Systems, 2(4), 230006. https://doi.org/10.2496.

[4] Lee, D., Lee, J. Y., Kim, D., Choi, J., & Kim, J. (2022). Fix the noise: Disentangling source feature for transfer learning of StyleGAN. arXiv preprint arXiv:2204.14079. https://arxiv.org/pdf/2204.14079

Type de contrat : stage

Durée du contrat : 6 mois

Niveau d’études requis : Bac+5

Expérience : non

Lieu de travail : CNRM Toulouse et à distance

Quotité du travail : 100%

Supervision :

Victor Sanchez (CNRM), Angélique Bonamy (CNRM) et Laure Raynaud (CNRM)

Pour postuler

Adresser CV + lettre de motivation :

victor.sanchez@meteo.fr

Stage : EXPLORATION DES SYNERGIES ENTRE MÉTHODES STATISTIQUES ET FORMELLES POUR L’EXPLICABILITÉ DE L’INTELLIGENCE ARTIFICIELLE – 21 octobre, 2024

Dans ce stage, nous nous pencherons sur la synergie entre deux domaines essentiels de l’explicabilité de l’intelligence artificielle : L’explicabilité statistique et l’explicabilité formelle. L’explicabilité statistique, en particulier par l’attribution de caractéristiques, a été la pierre angulaire de l’identification des caractéristiques significatives contribuant à une prédiction. Cette méthode s’est avérée efficace pour diverses architectures neuronales, offrant une évolutivité et une application généralisée.

Cependant, le manque de garanties dans les méthodes statistiques a limité leur utilisation pratique dans l’industrie. Pour y remédier, notre projet de stage propose une analyse comparative des cartes de caractéristiques générées par les méthodes statistiques et les méthodes formelles. En examinant ces deux familles de techniques d’explicabilité, nous visons à combler le fossé entre la robustesse théorique et l’applicabilité pratique.

Ce projet sera évalué à l’aide d’un ensemble de données industrielles libres axées sur des scénarios d’atterrissage visuels. Les résultats pourraient potentiellement améliorer la fiabilité et la capacité d’action des méthodes d’explicabilité dans les applications du monde réel.

Idéalement, ce stage d’une durée de 6 mois commencera en Mars 2025 (la période est communiquée à titre indicatif, et pourra être revue).

Tasks and Accountabilities :

Votre tuteur/tutrice vous aidera à identifier vos objectifs professionnels et vous accompagnera dans le développement de vos compétences.

Vos principales activités seront les suivantes :

- Conduire un état de l’art des méthodes d’explicabilité statistique et formelle.

- Développer les algorithmes de mise en pratique des méthodes les plus pertinentes.

- Appliquer les méthodes à un cas d’usage industrie

Ce stage vous permettra notamment de développer les compétences suivantes :

- Connaissance des différentes méthodes d’explicabilité pour l’intelligence artificielle.

- Développement dans un cadre d’application industriel.

- Travail en équipe.

Required skills

Vous préparez actuellement un diplôme de niveau Bac +5 dans le domaine de l’intelligence artificielle ou une discipline apparentée?

Vous possédez les compétences suivantes :

-

- Expérience en python et framework Machine Learning/Deep Learning (e.g. Keras/Tensorflow)

- Expérience sur certaines méthodes d’explicabilité

- Excellent niveau de communication, travail d’équipe

Compétences linguistiques :

- Anglais : Intermédiaire

- Français : Avancé

Type de contrat : stage

Durée du contrat : 6 months

Niveau d’études requis : Bac+5

Expérience : non

Lieu de travail : Toulouse

Quotité du travail : 100%

Supervision :

Boumazouza Ryma (Airbus) et Ducoffe Mélanie (Airbus)

Pour postuler

Adresser CV + lettre de motivation :

ryma.boumazouza@airbus.com

melanie.ducoffe@airbus.com

Internship : FORMAL VERIFICATION OF MACHINE LEARNING ALGORITHMS ON ADVANCED AVIONICS HARDWARE – October 15, 2024

Machine Learning (ML) plays a pivotal role in the development of autonomous systems, including future generations of aircraft that will integrate advanced algorithms for enhanced capabilities, such as vision-based autonomous landing for drones and commercial aircraft. While these algorithms perform efficiently in cloud or data center environments, deploying them on autonomous vehicles presents significant challenges—especially in ensuring safety. In the field of aeronautics, every function, whether ML-based or not, must meet rigorous safety standards, even in the event of hardware failures.

Vision-based perception systems, which are critical for autonomous operations, demand immense computational power and high-bandwidth communications (e.g., from cameras). However, current avionics processors lack the necessary capacity to handle such workloads. As a result, new processing architectures, such as Component-off- the-shelf (COTS) GPUs and many-core processors, will be essential. Before these can be deployed, it’s crucial to study their hardware failure modes, understand how these failures could affect the ML algorithms they support, and develop safeguards to ensure safe execution.

Several existing works, such as [1], [2], and [3], have addressed these issues by formally modeling platform behavior in the presence of faults, along with the mitigation strategies designed to reduce the impact of these faults. These models can be analyzed using solvers to determine if the mitigations are sufficient to guarantee safe hardware operation under specified conditions.

Preliminary research has identified the Versatile Tensor Accelerator (VTA [4]) as a suitable candidate for further exploration of this problem. VTA is open hardware, meaning its hardware description is fully accessible and customizable. It is described using Chisel [5], an advanced high-level hardware description language built on Scala [6].

[1] Guinebert, I., Barrilado, A., Delmas, K., Galtié, F., & Pagetti, C. (2022, June). Quality of Fault Injection Strategies on Hardware Accelerator. In International Conference on Computer Safety, Reliability, and Security (pp. 222-236). Cham: Springer International Publishing.

[2]Faure-Gignoux, A, Delmas, K, Gauffriau, A, Pagetti, C. (2024) Methodology for formal verification of hardware.safety strategies using SMT. International conference on embedded software (EMSOFT)

[3] Dobis, A., Laeufer, K., Damsgaard, H. J., Petersen, T., Rasmussen, K. J. H., Tolotto, E., … & Schoeberl, M. (2023). Verification of chisel hardware designs with chiselverify. Microprocessors and Microsystems, 96, 104737.

[4] https://github.com/apache/tvm-vta [5] https://www.chisel-lang.org/

Tasks and Accountabilities :

The primary goal of this internship is to evaluate the effectiveness of a set of pre-selected formal verification methods on the VTA. The key steps include:

-

- Conducting a literature review to identify the most promising formal verification methods from the pre- selected set.

- Gaining proficiency with the toolset required for functional and cycle-accurate simulation of VTA executions.

- Developing a framework to run small portions of deep neural networks (DNNs) on both functional and cycle-accurate simulators.

- Extending the framework to verify formal properties using the selected methods.

- Assessing the expressiveness and scalability of the approach, initially focusing on specific parts of theVTA, and, if feasible, expanding to the full accelerator.

- Based on the experiments, formulating recommendations for future theoretical and practicaldevelopments required for full-scale safety validation of VTA-like accelerators.

Required skills

-

- Hardware description languages (advanced)

- Compilation, Computing architectures (intermediate)

- Formal verification (notions)

- Programming (advanced)

Desired period

March to September 2025

Type de contrat : stage

Durée du contrat : 5-6 months (march to September 2025)

Gratification : 624,22€/month

Niveau d’études requis : Bac+5

Expérience : non

Lieu de travail : ONERA Toulouse: 2 Av. Marc Pélegrin, 31000 Toulouse. (Toulouse)

Quotité du travail : 100%

Supervision :

Kevin Delmas (ONERA) and Anthony Faure-Gignoux (ONERA)

Pour postuler

Adresser CV + lettre de motivation :

Kevin.delmas@onera.fr

Anthony.faure-gignoux@onera.fr